US009153172B2

# (12) United States Patent

Nathan et al.

(54) METHOD AND SYSTEM FOR PROGRAMMING AND DRIVING ACTIVE MATRIX LIGHT EMITTING DEVICE PIXEL HAVING A CONTROLLABLE SUPPLY VOLTAGE

(71) Applicant: Ignis Innovation Inc., Waterloo (CA)

(72) Inventors: **Arokia Nathan**, Cambridge (GB); **Gholamreza Chaji**, Waterloo (CA);

Peyman Servati, Vancouver (CA)

(73) Assignee: Ignis Innovation Inc., Waterloo (CA)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 13/744,843

(22) Filed: Jan. 18, 2013

(65) **Prior Publication Data**

US 2013/0162507 A1 Jun. 27, 2013

#### Related U.S. Application Data

(63) Continuation of application No. 13/243,065, filed on Sep. 23, 2011, now Pat. No. 8,378,938, which is a continuation of application No. 12/851,652, filed on Aug. 6, 2010, now Pat. No. 8,405,587, which is a continuation of application No. 11/298,240, filed on Dec. 7, 2005, now Pat. No. 7,800,565.

## (30) Foreign Application Priority Data

Dec. 7, 2004 (CA) ...... 2490858

(51) **Int. Cl.**

G09G 3/30 (2006.01) G09G 3/32 (2006.01) G09G 3/36 (2006.01) (10) **Patent No.:**

US 9,153,172 B2

(45) **Date of Patent:**

Oct. 6, 2015

(52) U.S. Cl.

(Continued)

(58) Field of Classification Search

(56) References Cited

U.S. PATENT DOCUMENTS

3,506,851 A 4/1970 Polkinghorn et al.

3,750,987 A 8/1973 Gobel

(Continued)

FOREIGN PATENT DOCUMENTS

AU 729652 6/1997 CA 1294034 1/1992

(Continued)

OTHER PUBLICATIONS

Ahnood et al.: "Effect of threshold voltage instability on field effect mobility in thin film transistors deduced from constant current measurements"; dated Aug. 2009.

(Continued)

Primary Examiner — Long D Pham

(74) Attorney, Agent, or Firm — Nixon Peabody LLP

### (57) ABSTRACT

Method and system for programming and driving active matrix light emitting device pixel is provided. The pixel is a voltage programmed pixel circuit, and has a light emitting device, a driving transistor and a storage capacitor. The pixel has a programming cycle having a plurality of operating cycles, and a driving cycle. During the programming cycle, the voltage of the connection between the OLED and the driving transistor is controlled so that the desired gate-source voltage of a driving transistor is stored in a storage capacitor.

## 13 Claims, 22 Drawing Sheets

# US 9,153,172 B2 Page 2

| (52) <b>U.S.</b> (   |                     | G0  | 9G2300/0852 (2013.01); G09G       |    | 323,631<br>323,832 |     | 11/2001<br>11/2001 | Juang<br>Nishizawa et al.           |

|----------------------|---------------------|-----|-----------------------------------|----|--------------------|-----|--------------------|-------------------------------------|

| CrC.                 |                     |     | 9262 (2013.01); G09G 2310/06      | 6, | 333,729            | В1  | 12/2001            | На                                  |

|                      |                     |     | 99G 2310/061 (2013.01); G09G      |    | 345,085<br>365,917 |     | 2/2002<br>4/2002   | Yeo et al.<br>Yamazaki              |

|                      | (2013.01),          | O.  | 2320/043 (2013.01)                |    | 373,453            |     | 4/2002             | Yudasaka                            |

|                      |                     |     | 2020/073 (2013.01)                |    | 384,427            |     | 5/2002             | Yamazaki et al.                     |

| (56)                 | Refe                | rei | ices Cited                        |    | 388,653            |     |                    | Goto et al.                         |

| ,                    |                     |     |                                   |    | 392,617<br>396,469 |     | 5/2002             | Gleason<br>Miwa et al.              |

|                      | U.S. PATE           | NΊ  | DOCUMENTS                         |    | 399,988            |     | 6/2002             | Yamazaki                            |

| 3,774,05             | 5 A 11/10           | 73  | Bapat                             | 6, | 414,661            | В1  | 7/2002             |                                     |

| 4,090,09             |                     |     | Nagami                            |    | 417,825            |     | 7/2002             |                                     |

| 4,354,16             | 2 A 10/19           | 82  | Wright                            |    | 420,758<br>420,834 |     | 7/2002             | Nakajima<br>Yamazaki et al.         |

| 4,758,83             |                     |     | Kasahara et al.                   |    | 420,988            |     |                    | Azami et al.                        |

| 4,963,86<br>4,975,69 |                     |     | Stewart<br>Lee                    |    | 430,496            |     | 8/2002             |                                     |

| 4,996,52             |                     |     | Bell et al.                       |    | 433,488<br>445,376 |     | 8/2002<br>9/2002   |                                     |

| 5,051,73             |                     |     | Hayashida et al.                  |    | 468,638            |     |                    | Jacobsen et al.                     |

| 5,134,38<br>5,153,42 |                     |     | Smith et al.<br>Hack et al.       | 6, | 473,065            | В1  | 10/2002            |                                     |

| 5,170,15             |                     |     | Shinya                            |    | 475,845            |     | 11/2002            | Kimura<br>Tanaka et al.             |

| 5,204,66             | 1 A 4/19            |     | Hack et al.                       |    | 489,952<br>501,098 |     | 12/2002<br>12/2002 | Yamazaki                            |

| 5,222,08             |                     |     | Plus                              |    | 501,466            |     |                    | Yamagishi et al.                    |

| 5,266,51<br>5,278,54 |                     |     | Robb et al.<br>Smith et al.       |    | 512,271            |     |                    | Yamazaki et al.                     |

| 5,408,26             |                     |     | Main                              |    | 518,594<br>522,315 |     |                    | Nakajima et al.<br>Ozawa et al.     |

| 5,498,88             |                     |     | Lee et al.                        |    | 524,895            |     |                    | Yamazaki et al.                     |

| 5,572,44<br>5,589,84 |                     |     | Lentz et al.<br>Lewis             | 6, | 531,713            | В1  | 3/2003             | Yamazaki                            |

| 5,619,03             |                     |     | Weisfield                         |    | 535,185            |     |                    | Kim et al.                          |

| 5,648,27             |                     |     | Hara et al.                       |    | 542,138<br>559,594 |     |                    | Shannon et al.<br>Fukunaga et al.   |

| 5,670,97             |                     |     | Bassetti et al.                   | ,  | 573,195            |     |                    | Yamazaki et al.                     |

| 5,686,93<br>5,691,78 |                     |     | Weisbrod<br>Numao et al.          | 6, | 573,584            | B1  |                    | Nagakari et al.                     |

| 5,701,50             |                     |     | Yamashita et al.                  |    | 576,926            |     |                    | Yamazaki et al.                     |

| 5,712,65             | 3 A 1/19            | 98  | Katoh et al.                      |    | 580,408<br>580,657 |     |                    | Bae et al.<br>Sanford et al.        |

| 5,714,96             |                     |     | Ikeda                             |    | 583,398            |     | 6/2003             |                                     |

| 5,744,82<br>5,745,66 |                     |     | Kousai et al.<br>Kolpatzik et al. |    | 583,775            |     |                    | Sekiya et al.                       |

| 5,747,92             |                     |     | Shanks et al.                     |    | 583,776<br>587,086 |     |                    | Yamazaki et al.<br>Koyama           |

| 5,748,16             |                     |     | Shieh et al.                      |    | 593,691            |     |                    | Nishi et al.                        |

| 5,758,12<br>5,784,04 |                     |     | Gray et al.<br>Ono et al.         | 6, | 594,606            | B2  | 7/2003             |                                     |

| 5,790,23             |                     |     | Matsuyama                         |    | 597,203            |     | 7/2003             |                                     |

| 5,815,30             | 3 A 9/19            | 98  | Berlin                            |    | 611,108<br>617,644 |     |                    | Kimura<br>Yamazaki et al.           |

| 5,835,37<br>5,870,07 |                     |     | Smith et al.<br>Kawahata          |    | 618,030            |     | 9/2003             | Kane et al.                         |

| 5,874,80             |                     |     | Garbuzov et al.                   |    | 639,244            |     |                    | Yamazaki et al.                     |

| 5,880,58             | 2 A 3/19            | 99  | Sawada                            |    | 661,180<br>661,397 |     |                    | Koyama<br>Mikami et al.             |

| 5,903,24             |                     |     | Irwin                             | 6, | 670,637            | B2  |                    | Yamazaki et al.                     |

| 5,917,28<br>5,923,79 | UA 6/19<br>4 A 7/10 |     | Burrows et al.<br>McGrath et al.  |    | 677,713            |     | 1/2004             | Sung                                |

| 5,949,39             |                     |     | Kim                               |    | 680,577<br>680,580 |     | 1/2004             | Inukai et al.                       |

| 5,952,78             |                     |     | Stewart et al.                    |    | 686,699            |     |                    | Yumoto                              |

| 5,990,62<br>6,023,25 |                     |     | Yamada et al.<br>Howard et al.    |    | 687,266            |     | 2/2004             |                                     |

| 6,069,36             |                     |     | Chow et al.                       |    | 690,000<br>690,344 |     | 2/2004<br>2/2004   | Muramatsu et al.<br>Takeuchi et al. |

| 6,091,20             |                     |     | Kawashima et al.                  |    | 693,388            |     |                    | Oomura                              |

| 6,097,36<br>6,100,86 |                     |     | Holloman<br>Lee et al.            |    | 693,610            |     | 2/2004             | Shannon et al.                      |

| 6,144,22             |                     |     |                                   |    | 694,248            |     | 2/2004             |                                     |

| 6,177,91             | 5 B1 1/20           |     | Beeteson et al.                   |    | 697,057<br>720,942 |     |                    | Koyama et al.<br>Lee et al.         |

| 6,229,50             |                     |     | Dawson et al.                     |    | 724,151            |     | 4/2004             |                                     |

| 6,229,50<br>6,232,93 |                     |     | Kane<br>Saito et al.              |    | 734,636            |     |                    | Sanford et al.                      |

| 6,246,18             |                     |     | Nishigaki                         |    | 738,034<br>738,035 |     | 5/2004<br>5/2004   | Kaneko et al.                       |

| 6,252,24             |                     |     | Sano et al.                       |    | 753,655            |     |                    | Shih et al.                         |

| 6,259,42<br>6,268,84 |                     |     | Kurogane<br>Cairns et al.         | 6, | 753,834            | B2  | 6/2004             | Mikami et al.                       |

| 6,274,88             |                     |     | Yamazaki et al.                   |    | 756,741            |     | 6/2004             |                                     |

| 6,288,69             | 6 B1 9/20           | 01  | Holloman                          |    | 771,028<br>777,712 |     |                    | Winters<br>Sanford et al.           |

| 6,300,92             |                     |     | Kim<br>Ohtoni et el               |    | 777,888            |     | 8/2004             |                                     |

| 6,303,96<br>6,306,69 |                     |     | Ohtani et al.<br>Yamazaki et al.  |    | 780,687            |     |                    | Nakajima et al.                     |

| 6,307,32             | 2 B1 10/20          | 01  | Dawson et al.                     | 6, | 781,567            | B2  | 8/2004             | Kimura                              |

| 6,310,96             |                     |     | Chung et al.                      |    | 788,231            |     | 9/2004             |                                     |

| 6,316,78<br>6,320,32 |                     |     | Mueller et al.<br>Cok et al.      |    | 806,638<br>806,857 |     |                    | Lih et al.<br>Sempel et al.         |

| 0,520,52             | J DI 11/20          | υI  | Ook of all                        | ο, | 000,037            | 102 | 10/2007            | Semper et al.                       |

# US 9,153,172 B2

Page 3

| (56)                 |       | Referen          | ces Cited                           | 7,485,478                    |       |                  | Yamagata et al.                    |        |

|----------------------|-------|------------------|-------------------------------------|------------------------------|-------|------------------|------------------------------------|--------|

|                      | 11.0  | DATENT           | DOCLINATENITO                       | 7,495,501                    |       |                  | Iwabuchi et al.<br>Yuki et al.     |        |

|                      | U.S.  | PATENT           | DOCUMENTS                           | 7,502,000<br>7,515,124       |       |                  | Yaguma et al.                      |        |

| 6,809,70             | )6 B2 | 10/2004          | Shimoda                             | 7,535,449                    |       |                  | Miyazawa                           |        |

| 6,828,95             |       |                  | Koyama                              | 7,554,512                    |       | 6/2009           | Steer                              |        |

| 6,858,99             |       |                  | Miyazawa                            | 7,569,849                    |       |                  | Nathan et al.                      |        |

| 6,859,19             | 93 B1 | 2/2005           | Yumoto                              | 7,595,776                    |       |                  | Hashimoto et al.                   |        |

| 6,861,67             |       |                  | Ohtani et al.                       | 7,604,718<br>7,609,239       |       | 10/2009          | Zhang et al.                       |        |

| 6,873,11             |       |                  | Ishizuka                            | 7,612,745                    |       |                  | Yumoto et al.                      |        |

| 6,873,32<br>6,876,34 |       |                  | Nakamura<br>Anzai et al.            | 7,619,594                    |       | 11/2009          |                                    |        |

| 6,878,96             |       |                  | Ohnuma                              | 7,619,597                    |       |                  | Nathan et al.                      |        |

| 6,900,48             |       | 5/2005           |                                     | 7,639,211                    |       |                  | Miyazawa                           |        |

| 6,903,73             |       | 6/2005           |                                     | 7,683,899<br>7,688,289       |       |                  | Hirakata et al.<br>Abe et al.      |        |

| 6,909,11<br>6,909,41 |       |                  | Yamazaki<br>Zavracky et al.         | 7,697,052                    |       |                  | Yamazaki et al.                    |        |

| 6,911,96             |       | 6/2005           | Yokoyama                            | 7,760,162                    |       |                  | Miyazawa                           |        |

| 6,911,96             |       |                  | Lee et al.                          | 7,808,008                    |       | 10/2010          |                                    |        |

| 6,914,44             | 48 B2 | 7/2005           |                                     | 7,825,419                    |       |                  | Yamagata et al.                    |        |

| 6,919,87             |       | 7/2005           |                                     | 7,859,520<br>7,868,859       |       | 1/2010           | Tomida et al.                      |        |

| 6,924,60<br>6,937,21 |       | 8/2005<br>8/2005 | Komiya                              | 7,876,294                    |       |                  | Sasaki et al.                      |        |

| 6,937,22             |       |                  | Kitaura et al.                      | 7,889,159                    |       |                  | Nathan et al.                      |        |

| 6,940,21             |       |                  | Komiya et al.                       | 7,903,127                    | B2    | 3/2011           |                                    |        |

| 6,943,50             |       |                  | LeChevalier                         | 7,920,116                    |       |                  | Woo et al.                         |        |

| 6,954,19             |       |                  | Matsumoto et al.                    | 7,944,414<br>7,969,390       |       |                  | Shirasaki et al.<br>Yoshida        |        |

| 6,956,54             |       |                  | Bae et al.                          | 7,978,170                    |       |                  | Park et al.                        |        |

| 6,970,14<br>6,975,14 |       |                  | Chung et al.<br>Azami et al.        | 7,989,392                    |       |                  | Crockett et al.                    |        |

| 6,975,33             |       |                  | Arnold et al.                       | 7,995,008                    |       | 8/2011           |                                    |        |

| 6,995,51             |       |                  | Murakami et al.                     | 7,995,010                    |       |                  | Yamazaki et al.                    |        |

| 6,995,51             |       |                  | Arnold et al.                       | 8,044,893                    |       |                  | Nathan et al.                      |        |

| 7,022,55             |       |                  | Adachi                              | 8,063,852<br>8,144,081       |       |                  | Kwak et al.<br>Miyazawa            |        |

| 7,023,40<br>7,027,01 |       |                  | Chen et al.<br>Booth, Jr. et al.    | 8,159,007                    |       |                  | Barna et al.                       |        |

| 7,034,79             |       |                  | Sekiya et al.                       | 8,242,979                    |       |                  | Anzai et al.                       |        |

| 7,038,39             | 92 B2 | 5/2006           | Libsch et al.                       | 8,319,712                    |       |                  | Nathan et al.                      |        |

| 7,057,58             |       |                  | Asano et al.                        | 8,493,295<br>8,497,525       |       |                  | Yamazaki et al.<br>Yamagata et al. |        |

| 7,061,45             |       |                  | Kimura                              | 2001/0002703                 |       | 6/2001           | Koyama                             |        |

| 7,071,93<br>7,088,05 |       | 8/2006           | Libsch et al.                       | 2001/0004190                 |       |                  | Nishi et al.                       |        |

| 7,106,28             |       |                  | Naugler                             | 2001/0009283                 |       |                  | Arao et al.                        |        |

| 7,112,82             |       |                  | Chang et al.                        | 2001/0020926                 |       | 9/2001           | 3                                  |        |

| 7,113,86             |       |                  | Smith et al.                        | 2001/0026127<br>2001/0026179 |       | 10/2001          | Yoneda et al.                      |        |

| 7,116,05             |       | 10/2006          | Lo et al.<br>Ikeda et al.           | 2001/0026179                 |       | 10/2001          |                                    |        |

| 7,122,83<br>7,129,91 |       |                  | Knapp et al.                        | 2001/0030323                 |       | 10/2001          |                                    |        |

| 7,141,82             |       | 11/2006          | Yamazaki et al.                     | 2001/0038098                 |       |                  | Yamazaki et al.                    |        |

| 7,164,41             | 17 B2 | 1/2007           | Cok                                 | 2001/0040541                 |       |                  | Yoneda et al.                      |        |

| 7,193,58             |       |                  | Yoshida et al.                      | 2001/0043173<br>2001/0045929 |       | 11/2001          |                                    |        |

| 7,199,51             |       |                  | Seo et al.                          | 2001/0043929                 |       |                  | Sempel et al.                      |        |

| 7,220,99<br>7,224,33 |       | 5/2007           | Nakata<br>Cok                       | 2001/0052898                 |       |                  | Osame et al.                       |        |

| 7,235,81             |       |                  | Yamazaki et al.                     | 2001/0052940                 |       |                  | Hagihara et al.                    |        |

| 7,245,27             |       |                  | Ishizuka                            | 2002/0000576                 |       | 1/2002           |                                    |        |

| 7,248,23             |       |                  | Nathan et al.                       | 2002/0011796<br>2002/0011799 |       |                  | Koyama<br>Kimura                   |        |

| 7,259,73<br>7,262,75 |       |                  | Ono et al.<br>Tanghe et al.         | 2002/0011793                 |       | 1/2002           |                                    |        |

| 7,274,34             |       |                  | Imamura et al.                      | 2002/0012057                 |       |                  | Kimura                             |        |

| 7,274,36             |       |                  | Ishizuka et al.                     | 2002/0015031                 |       |                  | Fujita et al.                      |        |

| 7,279,71             |       |                  | Yamazaki et al.                     | 2002/0015032                 |       |                  | Koyama et al.<br>Ohtani et al.     |        |

| 7,304,62             |       |                  | Oomori et al.                       | 2002/0030190<br>2002/0030528 |       |                  | Matsumoto et al.                   |        |

| 7,310,09<br>7,315,29 |       |                  | Imamura<br>Kimura                   | 2002/0030647                 |       |                  | Hack et al                         | 345/82 |

| 7,317,43             |       |                  | Lan et al.                          | 2002/0036463                 |       |                  | Yoneda et al.                      |        |

| 7,319,46             |       |                  | Mikami et al.                       | 2002/0047565                 |       |                  | Nara et al.                        |        |

| 7,321,34             | 48 B2 | 1/2008           | Cok et al.                          | 2002/0047852                 |       |                  | Inukai et al.                      |        |

| 7,327,35             |       | 2/2008           |                                     | 2002/0048829<br>2002/0050795 |       | 4/2002<br>5/2002 | Yamazaki et al.<br>Imura           |        |

| 7,333,07<br>7,339,63 |       |                  | Koyama et al.<br>Voloschenko et al. | 2002/0052086                 |       | 5/2002           |                                    |        |

| 7,339,03<br>7,343,24 |       |                  | Smith et al.                        | 2002/0052080                 |       |                  | Ishikawa et al.                    |        |

| 7,355,57             |       |                  | Leon et al.                         | 2002/0070909                 |       |                  | Asano et al.                       |        |

| 7,358,94             | 41 B2 | 4/2008           | Ono et al.                          | 2002/0080108                 |       | 6/2002           |                                    |        |

| 7,402,46             |       |                  | Kadono et al.                       | 2002/0084463                 |       |                  | Sanford et al.                     |        |

| 7,414,60             |       |                  | Nathan et al.                       | 2002/0101172                 |       | 8/2002           |                                    |        |

| 7,432,88             |       |                  | Asano et al.                        | 2002/0101433                 |       |                  | McKnight<br>Yamagata et al.        |        |

| 7,466,16<br>7,474,28 |       |                  | Date et al.<br>Kimura               | 2002/0113248<br>2002/0117722 |       |                  | Yamagata et al. Osada et al.       |        |

| 1,71,40              | 04    | 1/2003           | 1 x 1111 to 1 d                     | 2002/011/722                 | 4 7 1 | U, 2002          | Source et al.                      |        |

# US 9,153,172 B2

Page 4

| (56)                               | Referei          | nces Cited                           | 2004/0196275 A1                     | 10/2004            | Hattori                              |

|------------------------------------|------------------|--------------------------------------|-------------------------------------|--------------------|--------------------------------------|

|                                    | DATENIT          |                                      | 2004/0201554 A1<br>2004/0207615 A1  | 10/2004<br>10/2004 |                                      |

| 0.5.1                              | PALENI           | DOCUMENTS                            | 2004/0207013 A1<br>2004/0239596 A1  |                    | Ono et al.                           |

| 2002/0122308 A1                    | 9/2002           | Ikeda                                | 2004/0239696 A1                     | 12/2004            |                                      |

| 2002/0122506 A1                    |                  | Forbes                               | 2004/0251844 A1                     | 12/2004            | Hashido et al.                       |

| 2002/0140712 A1                    | 10/2002          | Ouchi et al.                         | 2004/0252085 A1                     |                    | Miyagawa                             |

| 2002/0154084 A1                    |                  | Tanaka et al.                        | 2004/0252089 A1                     |                    | Ono et al.<br>Yamada et al.          |

| 2002/0158587 A1                    | 10/2002          | Komiya                               | 2004/0256617 A1<br>2004/0257353 A1  |                    | Imamura et al.                       |

| 2002/0158666 A1<br>2002/0158823 A1 |                  | Azami et al.<br>Zavracky et al.      | 2004/0257355 A1                     | 12/2004            |                                      |

| 2002/0163314 A1                    |                  | Yamazaki et al.                      | 2004/0263437 A1                     | 12/2004            | Hattori                              |

| 2002/0171613 A1                    | 11/2002          | Goto et al.                          | 2005/0007357 A1                     |                    | Yamashita et al.                     |

| 2002/0180369 A1                    |                  | Koyama                               | 2005/0035709 A1<br>2005/0052379 A1  |                    | Furuie et al.<br>Waterman            |

| 2002/0180721 A1<br>2002/0186214 A1 |                  | Kimura et al.<br>Siwinski            | 2005/0057459 A1                     |                    | Miyazawa                             |

| 2002/0190332 A1                    |                  | Lee et al.                           | 2005/0067970 A1                     |                    | Libsch et al.                        |

| 2002/0190924 A1                    |                  | Asano et al.                         | 2005/0067971 A1                     | 3/2005             |                                      |

| 2002/0190971 A1                    |                  | Nakamura et al.                      | 2005/0068270 A1<br>2005/0083270 A1  |                    | Awakura<br>Miyazawa                  |

| 2002/0195967 A1<br>2002/0195968 A1 |                  | Kim et al.<br>Sanford et al.         | 2005/0085270 A1<br>2005/0088103 A1* |                    | Kageyama et al 315/169.3             |

| 2003/0001828 A1                    |                  | Asano                                | 2005/0110420 A1                     |                    | Arnold et al.                        |

| 2003/0020413 A1                    |                  | Oomura                               | 2005/0110727 A1                     | 5/2005             |                                      |

| 2003/0030603 A1                    |                  | Shimoda                              | 2005/0117096 A1<br>2005/0123193 A1  |                    | Voloschenko et al.<br>Lamberg et al. |

| 2003/0062524 A1<br>2003/0062844 A1 |                  | Kimura                               | 2005/0125193 A1<br>2005/0140598 A1  |                    | Kim et al.                           |

| 2003/0062844 A1<br>2003/0063081 A1 |                  | Miyazawa<br>Kimura et al.            | 2005/0140610 A1                     |                    | Smith et al.                         |

| 2003/0076048 A1                    |                  | Rutherford                           | 2005/0145891 A1                     | 7/2005             |                                      |

| 2003/0090445 A1                    |                  | Chen et al.                          | 2005/0156831 A1                     |                    | Yamazaki et al.                      |

| 2003/0090447 A1                    |                  | Kimura                               | 2005/0168416 A1<br>2005/0206590 A1  |                    | Hashimoto et al.<br>Sasaki et al.    |

| 2003/0090481 A1<br>2003/0095087 A1 |                  | Kimura<br>Libsch                     | 2005/0219188 A1                     |                    | Kawabe et al.                        |

| 2003/0098829 A1                    |                  | Chen et al.                          | 2005/0225686 A1                     | 10/2005            | Brummack et al.                      |

| 2003/0107560 A1                    |                  | Yumoto et al.                        | 2005/0243037 A1                     |                    | Eom et al.                           |

| 2003/0107561 A1                    |                  | Uchino et al.                        | 2005/0248515 A1<br>2005/0258867 A1  |                    | Naugler et al.<br>Miyazawa           |

| 2003/0111966 A1<br>2003/0112205 A1 |                  | Mikami et al.<br>Yamada              | 2005/0258807 A1<br>2005/0260777 A1  |                    | Brabec et al.                        |

| 2003/0112203 A1<br>2003/0112208 A1 |                  | Okabe et al.                         | 2005/0269959 A1                     |                    | Uchino et al.                        |

| 2003/0117348 A1                    |                  | Knapp et al.                         | 2005/0269960 A1                     |                    | Ono et al.                           |

| 2003/0122474 A1                    | 7/2003           |                                      | 2005/0285822 A1                     |                    | Reddy et al.<br>Eom et al.           |

| 2003/0122745 A1                    |                  | Miyazawa<br>Shannon et al.           | 2005/0285825 A1<br>2006/0007072 A1  |                    | Choi et al.                          |

| 2003/0122747 A1<br>2003/0128199 A1 |                  | Kimura                               | 2006/0012310 A1*                    |                    | Chen et al                           |

| 2003/0140958 A1                    |                  | Yang et al.                          | 2006/0012311 A1                     |                    | Ogawa                                |

| 2003/0151569 A1                    |                  | Lee et al.                           | 2006/0027807 A1<br>2006/0030084 A1  | 2/2006<br>2/2006   | Nathan et al.                        |

| 2003/0156104 A1                    |                  | Morita<br>LeChevalier                | 2006/0030084 A1<br>2006/0038750 A1  |                    | Inoue et al.                         |

| 2003/0169241 A1<br>2003/0169247 A1 |                  | Kawabe et al.                        | 2006/0038758 A1                     |                    | Routley et al.                       |

| 2003/0174152 A1                    |                  | Noguchi                              | 2006/0038762 A1                     | 2/2006             |                                      |

| 2003/0179626 A1                    |                  | Sanford et al.                       | 2006/0066527 A1<br>2006/0066533 A1  | 3/2006             | Chou<br>Sato et al.                  |

| 2003/0189535 A1                    |                  | Matsumoto et al.<br>Lee et al.       | 2006/0000333 A1<br>2006/0077077 A1  | 4/2006             |                                      |

| 2003/0197663 A1<br>2003/0214465 A1 |                  | Kimura                               | 2006/0092185 A1                     | 5/2006             | Jo et al.                            |

| 2003/0230980 A1                    |                  | Forrest et al.                       | 2006/0125408 A1                     |                    | Nathan et al.                        |

| 2004/0004589 A1                    | 1/2004           |                                      | 2006/0139253 A1<br>2006/0145964 A1  |                    | Choi et al.<br>Park et al.           |

| 2004/0027063 A1                    |                  | Nishikawa<br>Cok et al.              | 2006/0143964 A1<br>2006/0191178 A1  |                    | Sempel et al.                        |

| 2004/0032382 A1<br>2004/0041750 A1 | 3/2004           |                                      | 2006/0209012 A1                     | 9/2006             | Hagood, IV                           |

| 2004/0056604 A1                    |                  | Shih et al.                          | 2006/0221009 A1                     | 10/2006            |                                      |

| 2004/0066357 A1                    |                  | Kawasaki                             | 2006/0227082 A1<br>2006/0232522 A1  |                    | Ogata et al.<br>Roy et al.           |

| 2004/0070557 A1                    |                  | Asano et al.                         | 2006/0232322 A1<br>2006/0244391 A1  |                    | Shishido et al.                      |

| 2004/0080262 A1<br>2004/0080470 A1 |                  | Park et al.<br>Yamazaki et al.       | 2006/0244697 A1                     |                    | Lee et al.                           |

| 2004/0090400 A1                    | 5/2004           |                                      | 2006/0261841 A1                     | 11/2006            |                                      |

| 2004/0108518 A1                    | 6/2004           |                                      | 2006/0264143 A1                     |                    | Lee et al.                           |

| 2004/0113903 A1                    |                  | Mikami et al.                        | 2006/0273997 A1<br>2006/0284801 A1  |                    | Nathan et al.<br>Yoon et al.         |

| 2004/0129933 A1<br>2004/0130516 A1 |                  | Nathan et al.<br>Nathan et al.       | 2006/0290614 A1                     |                    | Nathan et al.                        |

| 2004/0135749 A1                    |                  | Kondakov et al.                      | 2007/0001937 A1                     |                    | Park et al.                          |

| 2004/0145547 A1                    | 7/2004           | Oh                                   | 2007/0001939 A1                     |                    | Hashimoto et al.                     |

| 2004/0150592 A1                    |                  | Mizukoshi et al.                     | 2007/0001945 A1<br>2007/0008268 A1  |                    | Yoshida et al.<br>Park et al.        |

| 2004/0150594 A1<br>2004/0150595 A1 | 8/2004<br>8/2004 | Koyama et al.<br>Kasai               | 2007/0008268 A1<br>2007/0008297 A1  |                    | Park et al.<br>Bassetti              |

| 2004/0155841 A1                    |                  | Kasai                                | 2007/00035489 A1                    | 2/2007             |                                      |

| 2004/0174347 A1                    |                  | Sun et al.                           | 2007/0035707 A1                     | 2/2007             | Margulis                             |

| 2004/0174349 A1*                   |                  | Libsch et al 345/204                 | 2007/0040773 A1                     |                    | Lee et al.                           |

| 2004/0174354 A1                    | 9/2004           |                                      | 2007/0063932 A1                     |                    | Nathan et al.                        |

| 2004/0183759 A1<br>2004/0189627 A1 |                  | Stevenson et al.<br>Shirasaki et al. | 2007/0069998 A1<br>2007/0080905 A1  |                    | Naugler et al.<br>Takahara           |

| 2007/010302/ AI                    | J. 2004          | omrasari et ar.                      | 2007/0000903 AI                     | 7/200/             | i unuitul a                          |

# **US 9,153,172 B2**Page 5

| (56)                               | Referen           | nces Cited                     |   | CA<br>CA | 2567076<br>2 495 726                     |             | 1/2006<br>7/2006  |

|------------------------------------|-------------------|--------------------------------|---|----------|------------------------------------------|-------------|-------------------|

| U.                                 | S. PATENT         | DOCUMENTS                      | ( | CA       | 2557713                                  | 7           | 11/2006           |

| 2007/0080906 A                     | 1 4/2007          | Tanabe                         |   | CA<br>CA | 2526782 C<br>2 651 893                   | _           | 8/2007<br>11/2007 |

| 2007/0080908 A                     | 1 4/2007          | Nathan et al.                  |   | CA<br>CN | 2 672 590                                |             | 10/2009           |

| 2007/0080918 A:<br>2007/0085801 A: |                   | Kawachi et al.<br>Park et al.  |   | DE       | 1381032<br>20 2006 005427                |             | 11/2002<br>6/2006 |

| 2007/0103419 A                     |                   | Uchino et al.                  | I | DE       | 202006007613                             |             | 9/2006            |

| 2007/0109232 A                     |                   | Yamamoto et al.                |   | EP<br>EP | 0 478 186<br>0 940 796                   |             | 4/1992<br>9/1999  |

| 2007/0128583 A<br>2007/0164941 A   |                   | Miyazawa<br>Park et al.        | I | EΡ       | 1 028 471 A                              | 4           | 8/2000            |

| 2007/0182671 A                     | 1 8/2007          | Nathan et al.                  |   | EP       | 1 103 947                                | A 1         | 5/2001            |

| 2007/0236430 A<br>2007/0241999 A   |                   |                                |   | EP<br>EP | 1 130 565 A<br>1 184 833                 | <b>A</b> 1  | 9/2001<br>3/2002  |

| 2007/0241999 A                     |                   |                                | I | EΡ       | 1 194 013                                |             | 3/2002            |

| 2007/0273294 A                     |                   | Nagayama                       |   | EP<br>EP | 0 925 588<br>1 310 939                   |             | 11/2002<br>5/2003 |

| 2007/0285359 A<br>2007/0296672 A   |                   | Ono<br>Kim et al.              |   | EΡ       | 1 321 922                                |             | 6/2003            |

| 2008/0001544 A                     | 1/2008            | Murakami et al.                |   | EP       | 1 335 430 A                              | <b>4</b> 1  | 8/2003            |

| 2008/0042948 A<br>2008/0043044 A   |                   | Yamashita et al.<br>Woo et al. |   | EP<br>EP | 1 372 136<br>1 381 019                   |             | 12/2003<br>1/2004 |

| 2008/0043044 A                     |                   | Naugler et al.                 | I | EΡ       | 1 418 566                                |             | 5/2004            |

| 2008/0055134 A                     | 1 3/2008          | Li et al.                      |   | EP<br>EP | 1 429 312                                |             | 6/2004<br>7/2004  |

| 2008/0055209 A<br>2008/0074360 A   |                   | Cok<br>Lu et al.               |   | EΡ       | 1 465 143 A                              |             | 10/2004           |

| 2008/0074413 A                     | 1 3/2008          | Ogura                          |   | EP       | 1 467 408                                |             | 10/2004           |

| 2008/0088549 A                     |                   | Nathan et al.                  |   | EP<br>EP | 1 473 689 <i>A</i><br>1 517 290 <i>A</i> | -           | 11/2004<br>3/2005 |

| 2008/0094426 A<br>2008/0122819 A   |                   | Kimpe<br>Cho et al.            |   | EΡ       | 1 521 203 A                              |             | 4/2005            |

| 2008/0228562 A                     |                   |                                |   | GB<br>GB | 2 205 431<br>2 399 935                   |             | 12/1988<br>9/2004 |

| 2008/0231641 A<br>2008/0290805 A   |                   | Miyashita<br>Yamada et al.     |   | зв<br>ЗВ | 2 460 018                                |             | 11/2009           |

| 2009/0009459 A                     |                   | Miyashita                      |   | IP       | 09 090405                                |             | 4/1997            |

| 2009/0015532 A                     |                   | Katayama et al.                |   | IP<br>IP | 10-153759<br>10-254410                   |             | 6/1998<br>9/1998  |

| 2009/0032807 A<br>2009/0121988 A   |                   |                                |   | ĪΡ       | 11 231805                                |             | 8/1999            |

| 2009/0146926 A                     | 1 6/2009          | Sung et al.                    |   | IP<br>IP | 11-282419                                |             | 10/1999           |

| 2009/0153459 A9<br>2009/0160743 A  |                   | Han et al.<br>Tomida et al.    |   | IP       | 2000/056847<br>2000-077192               |             | 2/2000<br>3/2000  |

| 2009/0174628 A                     |                   | Wang et al.                    |   | ΙP       | 2000-089198                              |             | 3/2000            |

| 2009/0201281 A                     |                   | ,                              |   | IP<br>IP | 2000-352941<br>2002-91376                |             | 12/2000<br>3/2002 |

| 2009/0213046 A<br>2009/0251486 A   |                   | Nam<br>Sakakibara et al.       |   | ΙΡ       | 2002-268576                              |             | 9/2002            |

| 2009/0278777 A                     |                   | Wang et al.                    |   | IP<br>IP | 2002-278513                              |             | 9/2002            |

| 2010/0039451 A                     |                   | Jung                           |   | IP<br>IP | 2002-333862<br>2003-022035               |             | 11/2002<br>1/2003 |

| 2010/0039453 A                     |                   | Nathan et al.<br>Tanaka        |   | ΙP       | 2003-076331                              |             | 3/2003            |

| 2010/0079711 A:<br>2010/0207920 A: |                   | Chaji et al.                   |   | IP<br>IP | 2003-150082<br>2003-177709               |             | 5/2003<br>6/2003  |

| 2010/0225634 A                     | 9/2010            | Levey et al.                   |   | ΙΡ       | 2003-271095                              |             | 9/2003            |

| 2010/0269889 A                     |                   | Reinhold et al.                |   | IP<br>IP | 2003-308046                              |             | 10/2003           |

| 2010/0277400 A<br>2010/0315319 A   |                   | Jeong<br>Cok et al.            |   | IP<br>IP | 2004-054188<br>2005-057217               |             | 2/2004<br>3/2005  |

| 2010/0328294 A                     | 1 12/2010         | Sasaki et al.                  |   | ΙP       | 2005-099715                              |             | 4/2005            |

| 2011/0069089 A                     |                   | Kopf et al.                    |   | IP<br>ΓW | 2005-338819<br>485337                    |             | 12/2005<br>5/2002 |

| 2011/0090210 A                     | 1 4/2011          | Sasaki et al.                  |   | ΓW       | 502233                                   |             | 9/2002            |

| FORE                               | EIGN PATE         | NT DOCUMENTS                   |   | ΓW<br>ΓW | 538650<br>569173                         |             | 6/2003<br>1/2004  |

|                                    | 100.051           | 11/1002                        |   | ΓW       | 200526065                                |             | 8/2005            |

|                                    | 109 951<br>249592 | 11/1992<br>7/1998              |   | ΓW       | 1239501                                  |             | 9/2005            |

| CA 2.3                             | 303 302           | 3/1999                         |   | WO<br>WO | WO 94/25954<br>WO 99/48079               |             | 11/1994<br>9/1999 |

|                                    | 368386            | 9/1999                         | 7 | WO       | WO 9948079                               |             | 9/1999            |

|                                    | 242720<br>354018  | 1/2000<br>6/2000               |   | WO<br>WO | WO 01/27910 A<br>02/067327 A             |             | 4/2001<br>8/2002  |

| CA 2                               | 432530            | 7/2002                         |   | WO       | WO 03/034389                             | 1           | 4/2003            |

|                                    | 438 577<br>436451 | 8/2002<br>8/2002               |   | WO       | WO 03/063124                             |             | 7/2003            |

| CA 2                               | 507276            | 8/2002                         |   | WO<br>WO | WO 03/075256<br>WO 03/077231             |             | 9/2003<br>9/2003  |

|                                    | 483 645<br>463653 | 12/2003                        |   | WO       | WO 03/07/231<br>WO 03/105117             |             | 12/2003           |

|                                    | 463653<br>498136  | 1/2004<br>3/2004               |   | WO       | WO 2004/003877                           |             | 1/2004            |

| CA 2                               | 522396            | 11/2004                        |   | WO<br>WO | WO 2004/015668 A<br>WO 2004/034364       | <b>4</b> 1  | 2/2004<br>4/2004  |

|                                    | 438363<br>443206  | 2/2005<br>3/2005               |   | WO       | WO 2004/034304<br>WO 2005/022498         |             | 3/2004            |

| CA 2                               | 519097            | 3/2005                         | 7 | WO       | WO 2005/029455                           |             | 3/2005            |

|                                    | 472671            | 12/2005                        |   | WO<br>WO | WO 2005/055185                           | <b>A.</b> 1 | 6/2005<br>6/2005  |

| CA 2                               | 523841            | 1/2006                         | ` | WU       | WO 2005/055186 A                         | 7.1         | 0/2003            |

#### (56)References Cited

#### FOREIGN PATENT DOCUMENTS

| WO | WO 2005/069267 | 7/2005  |

|----|----------------|---------|

| WO | WO 2005/122121 | 12/2005 |

| WO | 2006/053424    | 5/2006  |

| WO | WO 2006/063448 | 6/2006  |

| WO | WO 2006/128069 | 11/2006 |

| WO | WO 2006/137337 | 12/2006 |

| WO | WO 2007/079572 | 7/2007  |

| WO | WO 2009/059028 | 5/2009  |

| WO | WO 2009/127065 | 10/2009 |

| WO | WO 2010/023270 | 3/2010  |

| WO | WO 2010/066030 | 6/2010  |

| WO | WO 2010/120733 | 10/2010 |

## OTHER PUBLICATIONS

Alexander et al.: "Pixel circuits and drive schemes for glass and elastic AMOLED displays"; dated Jul. 2005 (9 pages).

Alexander et al.: "Unique Electrical Measurement Technology for Compensation, Inspection, and Process Diagnostics of AMOLED HDTV"; dated May 2010 (4 pages).

Ashtiani et al.: "AMOLED Pixel Circuit With Electronic Compensation of Luminance Degradation"; dated Mar. 2007 (4 pages).

Chaji et al.: "A Current-Mode Comparator for Digital Calibration of Amorphous Silicon AMOLED Displays"; dated Jul. 2008 (5 pages). Chaji et al.: "A fast settling current driver based on the CCII for AMOLED displays"; dated Dec. 2009 (6 pages).

Chaji et al.: "A Low-Cost Stable Amorphous Silicon AMOLED Display with Full V~T- and V~O~L~E~D Shift Compensation"; dated May 2007 (4 pages).

Chaji et al.: "A low-power driving scheme for a-Si:H active-matrix organic light-emitting diode displays"; dated Jun. 2005 (4 pages).

Chaji et al.: "A low-power high-performance digital circuit for deep submicron technologies"; dated Jun. 2005 (4 pages).

Chaji et al.: "A novel a-Si:H AMOLED pixel circuit based on shortterm stress stability of a-Si:H TFTs"; dated Oct. 2005 (3 pages).

Chaji et al.: "A Novel Driving Scheme and Pixel Circuit for AMOLED Displays"; dated Jun. 2006 (4 pages).

Chaji et al.: "A novel driving scheme for high-resolution large-area a-Si:H AMOLED displays"; dated Aug. 2005 (4 pages)

Chaji et al.: "A Stable Voltage-Programmed Pixel Circuit for a-Si:H AMOLED Displays"; dated Dec. 2006 (12 pages).

Chaji et al.: "A Sub-µA fast-settling current-programmed pixel circuit for AMOLED displays"; dated Sep. 2007.

Chaji et al.: "An Enhanced and Simplified Optical Feedback Pixel Circuit for AMOLED Displays"; dated Oct. 2006.

Chaji et al.: "Compensation technique for DC and transient instability of thin film transistor circuits for large-area devices"; dated Aug. 2008.

Chaji et al.: "Driving scheme for stable operation of 2-TFT a-Si AMOLED pixel"; dated Apr. 2005 (2 pages).

Chaji et al.: "Dynamic-effect compensating technique for stable a-Si:H AMOLED displays"; dated Aug. 2005 (4 pages)

Chaji et al.: "Electrical Compensation of OLED Luminance Degradation"; dated Dec. 2007 (3 pages).

Chaji et al.: "eUTDSP: a design study of a new VLIW-based DSP architecture"; dated May 2003 (4 pages).

Chaji et al.: "Fast and Offset-Leakage Insensitive Current-Mode Line Driver for Active Matrix Displays and Sensors"; dated Feb. 2009 (8

Chaji et al.: "High Speed Low Power Adder Design With a New Logic Style: Pseudo Dynamic Logic (SDL)"; dated Oct. 2001 (4 pages).

Chaji et al.: "High-precision, fast current source for large-area current-programmed a-Si flat panels"; dated Sep. 2006 (4 pages).

Chaji et al.: "Low-Cost AMOLED Television with IGNIS Compensating Technology"; dated May 2008 (4 pages).

Chaji et al.: "Low-Cost Stable a-Si:H AMOLED Display for Portable Applications"; dated Jun. 2006 (4 pages). Chaji et al.: "Low-Power Low-Cost Voltage-Programmed a-Si:H

AMOLED Display"; dated Jun. 2008 (5 pages).

Chaji et al.: "Merged phototransistor pixel with enhanced near infrared response and flicker noise reduction for biomolecular imaging"; dated Nov. 2008 (3 pages).

Chaji et al.: "Parallel Addressing Scheme for Voltage-Programmed Active-Matrix OLED Displays"; dated May 2007 (6 pages).

Chaji et al.: "Pseudo dynamic logic (SDL): a high-speed and lowpower dynamic logic family"; dated Sep. 2002 (4 pages).

Chaji et al.: "Stable a-Si:H circuits based on short-term stress stability of amorphous silicon thin film transistors"; dated May 2006 (4 pages).

Chaji et al.: "Stable Pixel Circuit for Small-Area High- Resolution a-Si:H AMOLED Displays"; dated Oct. 2008 (6 pages).

Chaji et al.: "Stable RGBW AMOLED display with OLED degradation compensation using electrical feedback"; dated Feb. 2010 (2

Chaji et al.: "Thin-Film Transistor Integration for Biomedical Imaging and AMOLED Displays"; dated May 2008 (177 pages).

Jafarabadiashtiani et al.: "A New Driving Method for a-Si AMOLED Displays Based on Voltage Feedback"; dated May 2005 (4 pages). Lee et al.: "Ambipolar Thin-Film Transistors Fabricated by PECVD Nanocrystalline Silicon"; dated May 2006 (6 pages).

Ma e y et al: "Organic Light-Emitting Diode/Thin Film Transistor Integration for foldable Displays" Conference record of the 1997 International display research conference and international workshops on LCD technology and emissive technology. Toronto, Sep. 15-19, 1997 (6 pages).

Matsueda y et al.: "35.1: 2.5-in. AMOLED with Integrated 6-bit Gamma Compensated Digital Data Driver"; dated May 2004 (4

Nathan et al.: "Backplane Requirements for Active Matrix Organic Light Emitting Diode Displays"; dated Sep. 2006 (16 pages).

Nathan et al.: "Call for papers second international workshop on compact thin-film transistor (TFT) modeling for circuit simulation"; dated Sep. 2009 (1 page).

Nathan et al.: "Driving schemes for a-Si and LTPS AMOLED displays"; dated Dec. 2005 (11 pages).

Nathan et al.: "Invited Paper: a-Si for AMOLED—Meeting the Performance and Cost Demands of Display Applications (Cell Phone to HDTV)", dated Jun. 2006 (4 pages).

Nathan et al.: "Thin film imaging technology on glass and plastic"; dated Oct. 31-Nov. 2, 2000 (4 pages).

Philipp: "Charge transfer sensing" Sensor Review, vol. 19, No. 2, Dec. 31, 1999, 10 pages.

Rafati et al.: "Comparison of a 17 b multiplier in Dual-rail domino and in Dual-rail D L (D L) logic styles"; dated 2002 (4 pages)

Safavaian et al.: "Three-TFT image sensor for real-time digital X-ray imaging"; dated Feb. 2, 2006 (2 pages).

Safavian et al.: "3-TFT active pixel sensor with correlated double sampling readout circuit for real-time medical x-ray imaging"; dated Jun. 2006 (4 pages).

Safavian et al.: "A novel current scaling active pixel sensor with correlated double sampling readout circuit for real time medical x-ray imaging"; dated May 2007 (7 pages).

Safavian et al.: "A novel hybrid active-passive pixel with correlated double sampling CMOS readout circuit for medical x-ray imaging"; dated May 2008 (4 pages).

Safavian et al.: "Self-compensated a-Si:H detector with currentmode readout circuit for digital X-ray fluoroscopy"; dated Aug. 2005 (4 pages).

Safavian et al.: "TFT active image sensor with current-mode readout circuit for digital x-ray fluoroscopy [5969D-82]"; dated Sep. 2005 (9

Stewart M. et al., "Polysilicon TFT technology for active matrix OLED displays" IEEE transactions on electron devices, vol. 48, No. 5 May 2001 (7 pages).

Vygranenko et al.: "Stability of indium-oxide thin-film transistors by reactive ion beam assisted deposition"; dated Feb. 2009.

Wang et al.: "Indium oxides by reactive ion beam assisted evaporation: From material study to device application"; dated Mar. 2009 (6

Extended European Search Report mailed Nov. 8, 2011 issued in corresponding European Patent Application No. 11175223.4 (8 pages).

#### (56) References Cited

#### OTHER PUBLICATIONS

Chapter 3: Color Spaces" Keith Jack: "Video Demystified: "A Handbook for the Digital Engineer" 2001 Referex ORD-0000-00-00 USA EP040425529 ISBN: 1-878707-56-6 pp. 32-33.

Chapter 8: Alternative Flat Panel Display 1-25 Technologies; Willem den Boer: "Active Matrix Liquid Crystal Display: Fundamentals and Applications" 2005 Referex ORD-0000-00-00 U.K.; XP040426102 ISBN: 0-7506-7813-5 pp. 206-209 p. 208.

European Partial Search Report corresponding to European Patent Application Serial No. 12156251.6 European Patent Office dated May 30, 2012 (7 pages).

European Patent Office Communication in European Application No. 05821114 dated Jan. 11, 2013 (9 pages).

European Patent Office Communication with Supplemental European Search Report for EP Application No. 07701644.2 dated Aug. 18, 2009 (12 pages).

European Search Report and Written Opinion for Application No. 08 86 5338 mailed Nov. 2, 2011 (7 pages).

European Search Report corresponding to Application EP 10175764 dated Oct. 18, 2010 (2 pages).

European Search Report corresponding to European Patent Application Serial No. 12156251.6 European Patent Office dated Oct. 12, 2012 (18 pages).

European Search Report corresponding to European Patent Application No. 10829593.2 European Patent Office dated May 17, 2013 (7 pages)

European Search Report for Application No. 11175225.9 dated Nov. 4, 2011 (9 pages).

European Search Report for European Application No. EP 04 78 6661 dated Mar. 9, 2009.

European Search Report for European Application No. EP 05 75 9141 dated Oct. 30, 2009.

European Search Report for European Application No. EP 05 80 7905 dated Apr. 2, 2009 (5 pages).

European Search Report for European Application No. EP 05 82 1114 dated Mar. 27, 2009 (2 pages).

European Search Report for European Application No. EP 07 71 9579 dated May 20, 2009.

European Search Report for European Application Serial No. 12156251.6 dated Oct. 12, 2012 (18 pages).

European Search Report mailed Mar. 26, 2012 in corresponding European Patent Application No. 10000421.7 (6 pages).

European Search Report Application No. 10834294.0-1903 dated Apr. 8, 2013 (9 pages).

European Supplementary Search Report for EP 09 80 2309 dated May 8, 2011 (14 pages).

European Supplementary Search Report for European Application No. 00831330 8 dated Mar. 26, 2012 (11 pages)

No. 09831339.8 dated Mar. 26, 2012 (11 pages). Extended European Search Report corresponding to European Patent Application No. 12174465.0 European Patent Office dated Sep. 7,

2012 (9 pages). Extended European Search Report mailed Apr. 27, 2011 issued during prosecution of European patent application No. 09733076.5 (13

pages). Extended European Search Report Application No. 06752777.0 dated Dec. 6, 2010 (21 pages).

Extended European Search Report Application No. 09732338.0 dated May 24, 2011 (8 pages).

Fan et al. "LTPS\_TFT Pixel Circuit Compensation for TFT Threshold Voltage Shift and IR-Drop on the Power Line for Amolded Displays" 5 pages copyright 2012.

Goh et al. "A New a-Si:H Thin-Film Transistor Pixel Circuit for Active-Matrix Organic Light-Emitting Diodes" IEEE Electron Device Letters vol. 24 No. 9 Sep. 2003 pp. 583-585.

International Search Report for International Application No. PCT/CA2005/001844 dated Mar. 28, 2006 (2 pages).

International Search Report corresponding to International Patent Application No. PCT/IB2010/002898 Canadian Intellectual Property Office dated Jul. 28, 2009 (5 pages).

International Search Report for International Application No. PCT/CA2007/000013 dated May 7, 2007.

International Search Report for International Application No. PCT/CA2006/000941 dated Oct. 3, 2006 (2 pages).

International Search Report for International Application No. PCT/CA2009/001769 dated Apr. 8, 2010.

International Search Report for International Application No. PCT/CA02/00180 dated Jul. 31, 2002 (3 pages).

International Search Report for International Application No. PCT/CA2004/001741 dated Feb. 21, 2005.

International Search Report for International Application No. PCT/CA2005/001007 dated Oct. 18, 2005.

International Search Report for International Application No. PCT/CA2007/000652 dated Jul. 25, 2007.

International Search Report for International Application No. PCT/CA2008/002307 mailed Apr. 28, 2009 (3 pages).

International Search Report for International Application No. PCT/IB2011/055135 Canadian Patent Office dated Apr. 16, 2012 (5 pages)

International Search Report issued in International Application No. PCT/CA2009/001049 mailed Dec. 7, 2009 (4 pages).

International Search Report mailed Jul. 30, 2009 for International Application No. PCT/CA2009/000501 (4 pages).

International Search Report International Application PCT/IB2012/052651 5 pages dated, Sep. 11, 2012.

International Search Report PCT/IB2011/051103 dated Jul. 8, 2011, 3 pages.

International Searching Authority Search Report PCT/IB2010/055481 dated Apr. 7, 2011 (3 pages).

International Written Opinion International Application PCT/IB2012/052651 6 pages dated Sep. 11, 2012.

International Written Opinion PCT/IB2011/051103 dated Jul. 8, 2011, 6 pages.

Nathan et al. "Amorphous Silicon Thin Film Transistor Circuit Integration for Organic LED Displays on Glass and Plastic" IEEE Journal of Solid-State Circuits vol. 39 No. 9 Sep. 2004, pp. 1477-1486. Machine English translation of JP 2002-333862, 49 pages.

Office Action issued in Chinese Patent Application 200910246264.4 Dated Jul. 5, 2013; 8 pages.

Ono et al. "Shared Pixel Compensation Circuit for AM-OLED Displays" Proceedings of the 9<sup>th</sup> Asian Symposium on Information Display (ASID) pp. 462-465 New Delhi dated Oct. 8-12, 2006 (4 pages).

Patent Abstracts of Japan vol. 2000 No. 09, Oct. 13, 2000—JP 2000 172199 A, Jun. 3, 2000 abstract.

Patent Abstracts of Japan vol. 2002 No. 03 Apr. 3, 2002 (Apr. 4, 2004 & JP 2001 318627 A (Semiconductor EnergyLab DO Ltd) Nov. 16, 2001 abstract paragraphs '01331-01801 paragraph '01691 paragraph '01701 paragraph '01721 and figure 10.

Sanford James L. et al. "4.2 TFT AMOLED Pixel Circuits and Driving Methods" SID 03 Digest SSN/0003 2003, pp. 10-13.

Tatsuya Sasaoka et al. 24.4L; Late-News Paper: A 13.0-inch AM-Oled Display with Top Emitting Structure and Adaptive Current Mode Programmed Pixel Circuit (TAC) SID 01 Digest (2001) pp. 384-387.

Written Opinion corresponding to International Patent Application No. PCT/IB2010/002898 Canadian Intellectual Property Office dated Mar. 30, 2011 (8 pages).

Written Opinion for International Application No. PCT/CA2009/001769 dated Apr. 8, 2010 (8 pages).

Written Opinion mailed Jul. 30, 2009 for International Application No. PCT/CA2009/000501 (6 pages).

Yi He et al. "Current-Source a-Si:H Thin Film Transistor Circuit for Active-Matrix Organic Light-Emitting Displays" IEEE Electron Device Letters vol. 21 No. 12 Dec. 2000 pp. 590-592.

Zhiguo Meng et al; "24.3: Active-Matrix Organic Light-Emitting Diode Display implemented Using Metal-Induced Unilaterally Crystallized Polycrystalline Silicon Thin-Film Transistors" SID 01 Digest (2001) pp. 380-383.

<sup>\*</sup> cited by examiner

Figure 1

Prior Art

Figure 2

Figure 3

Figure 4

Figure 5

Figure 6

Figure 7(b)

Oct. 6, 2015

Figure 8

Figure 9

Figure 10

Figure 11

Figure 12

Figure 13

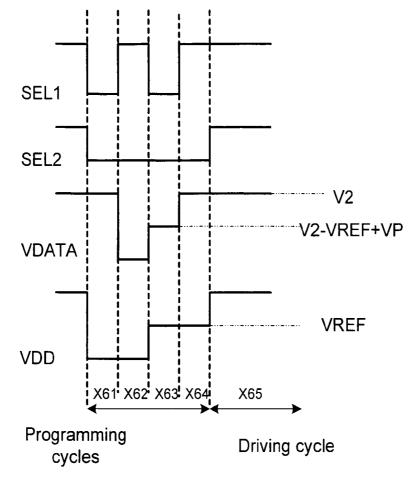

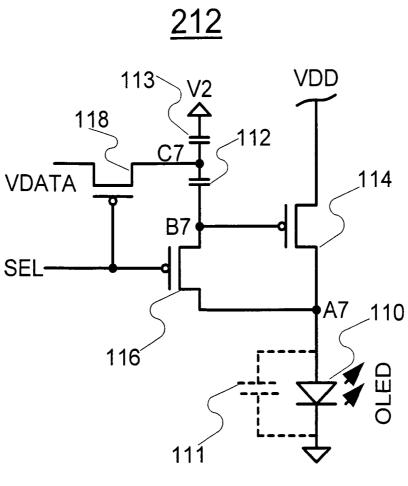

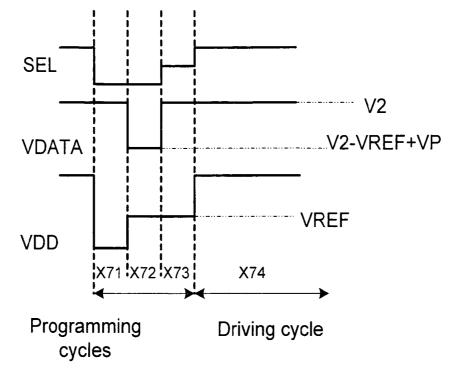

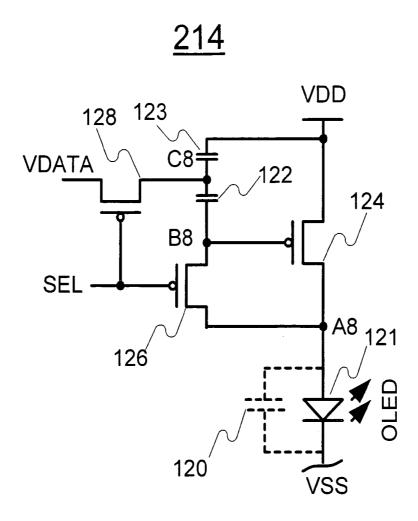

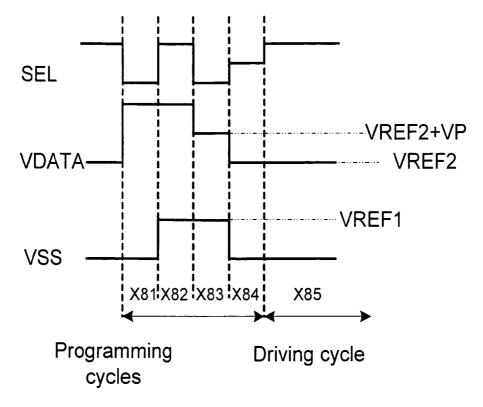

Driving cycle

Programming cycles

Figure 14

Figure 15

Figure 16

Figure 17

Figure 18

Figure 19

Figure 20

Figure 21

Figure 22

### METHOD AND SYSTEM FOR PROGRAMMING AND DRIVING ACTIVE MATRIX LIGHT EMITTING DEVICE PIXEL HAVING A CONTROLLABLE SUPPLY VOLTAGE

# CROSS REFERENCE TO RELATED APPLICATIONS

This application is a continuation of U.S. patent application Ser. No. 13/243,065, filed Sep. 23, 2011, which is a continuation of U.S. patent application Ser. No. 12/851,652, filed Aug. 6, 2010; which is a continuation of U.S. patent application Ser. No. 11/298,240, filed Dec. 7, 2005, now issued as U.S. Pat. No. 7,800,565, which claims priority to Canadian Patent No. 2,490,858, filed Dec. 7, 2004, each of which is incorporated herein by reference in its entirety.

#### FIELD OF INVENTION

The present invention relates to a light emitting device displays, and more specifically to a driving technique for the light emitting device displays.

#### BACKGROUND OF THE INVENTION

Recently active-matrix organic light-emitting diode (AMOLED) displays with amorphous silicon (a-Si), polysilicon, organic, or other driving backplane have become more attractive due to advantages over active matrix liquid 30 crystal displays. An AMOLED display using a-Si backplanes, for example, has the advantages which include low temperature fabrication that broadens the use of different substrates and makes flexible displays feasible, and its low cost fabrication that yields high resolution displays with a wide viewing 35 angle.

The AMOLED display includes an array of rows and columns of pixels, each having an organic light-emitting diode (OLED) and backplane electronics arranged in the array of rows and columns. Since the OLED is a current driven device, 40 the pixel circuit of the AMOLED should be capable of providing an accurate and constant drive current.

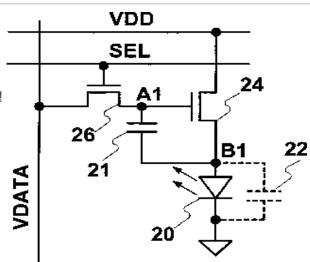

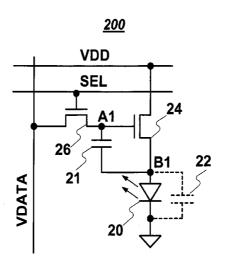

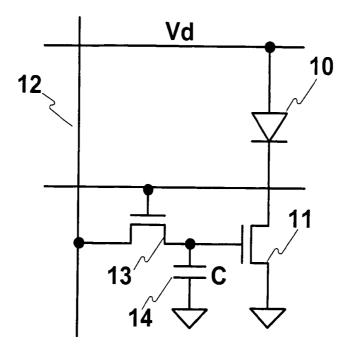

FIG. 1 shows a pixel circuit as disclosed in U.S. Pat. No. 5,748,160. The pixel circuit of FIG. 1 includes an OLED 10, a driving thin film transistor (TFT) 11, a switch TFT 13, and 45 a storage capacitor 14. The drain terminal of the driving TFT 11 is connected to the OLED 10. The gate terminal of the driving TFT 11 is connected to a column line 12 through the switch TFT 13. The storage capacitor 14, which is connected between the gate terminal of the driving TFT 11 and the 50 ground, is used to maintain the voltage at the gate terminal of the driving TFT 11 when the pixel circuit is disconnected from the column line 12. The current through the OLED 10 strongly depends on the characteristic parameters of the driving TFT 11. Since the characteristic parameters of the driving 55 TFT 11, in particular the threshold voltage under bias stress, vary by time, and such changes may differ from pixel to pixel, the induced image distortion may be unacceptably high.

U.S. Pat. No. 6,229,508 discloses a voltage-programmed pixel circuit which provides, to an OLED, a current independent of the threshold voltage of a driving TFT. In this pixel, the gate-source voltage of the driving TFT is composed of a programming voltage and the threshold voltage of the driving TFT. A drawback of U.S. Pat. No. 6,229,508 is that the pixel circuit requires extra transistors, and is complex, which 65 results in a reduced yield, reduced pixel aperture, and reduced lifetime for the display.

2

Another method to make a pixel circuit less sensitive to a shift in the threshold voltage of the driving transistor is to use current programmed pixel circuits, such as pixel circuits disclosed in U.S. Pat. No. 6,734,636. In the conventional current programmed pixel circuits, the gate-source voltage of the driving TFT is self-adjusted based on the current that flows through it in the next frame, so that the OLED current is less dependent on the current-voltage characteristics of the driving TFT. A drawback of the current-programmed pixel circuit is that an overhead associated with low programming current levels arises from the column line charging time due to the large line capacitance.

#### SUMMARY OF THE INVENTION

It is an object of the invention to provide a method and system that obviates or mitigates at least one of the disadvantages of existing systems.

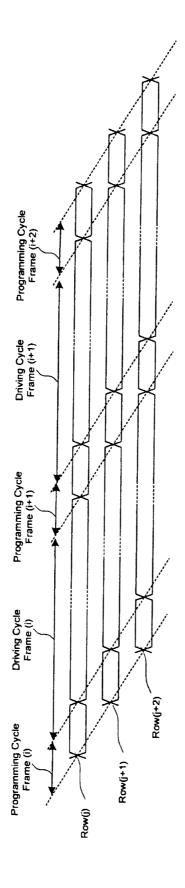

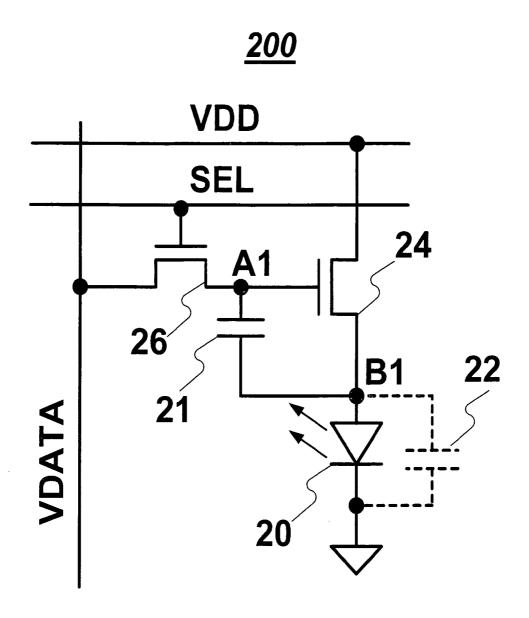

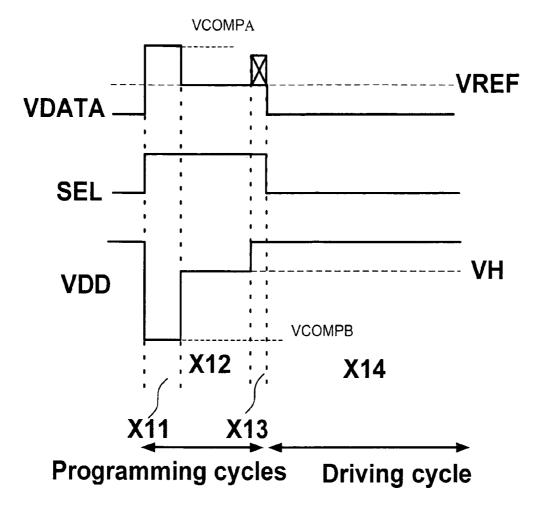

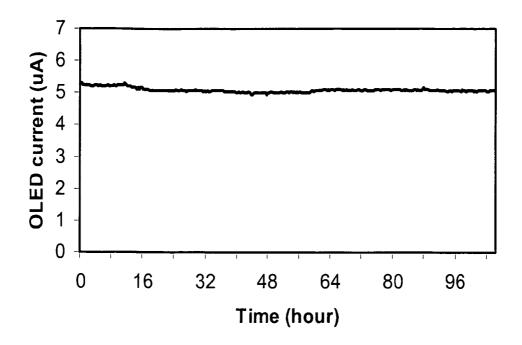

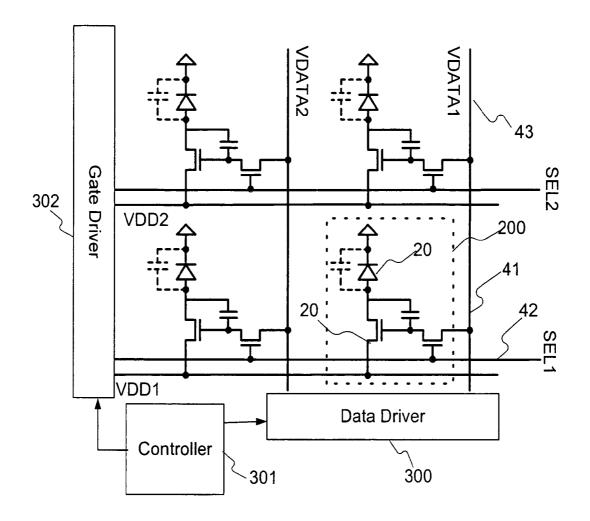

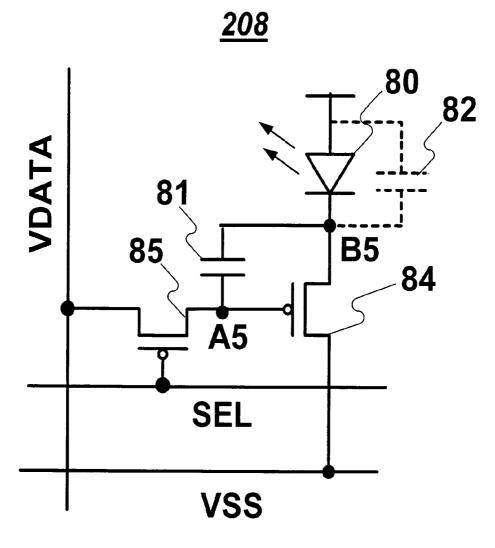

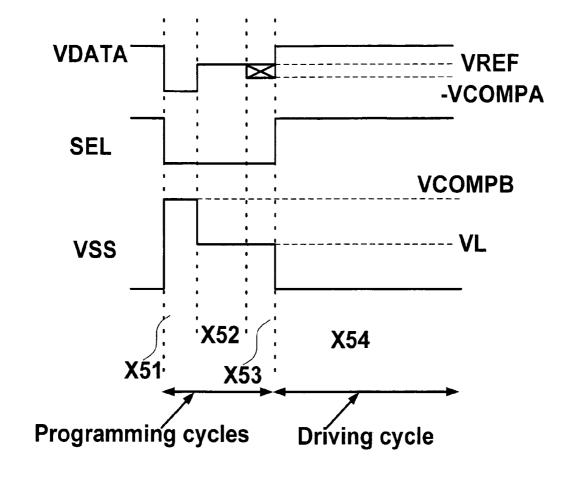

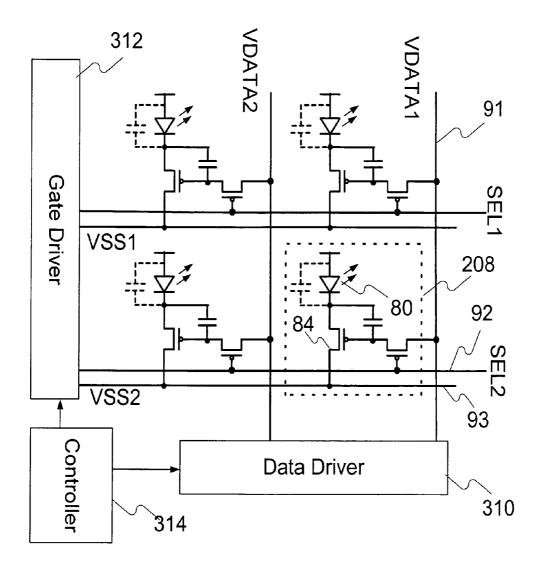

In accordance with an aspect to the present invention there 20 is provided a method of programming and driving a display system, the display system includes: a display array having a plurality of pixel circuits arranged in row and column, each pixel circuit having: a light emitting device having a first terminal and a second terminal, the first terminal of the light-25 ing device being connected to a voltage supply electrode; a capacitor having a first terminal and a second terminal; a switch transistor having a gate terminal, a first terminal and a second terminal, the gate terminal of the switch transistor being connected to a select line, the first terminal of the switch transistor being connected to a signal line for transferring voltage data, the second terminal of the switch transistor being connected to the first terminal of the capacitor; and a driving transistor having a gate terminal, a first terminal and a second terminal, the gate terminal of the driving transistor being connected to the second terminal of the switch transistor and the first terminal of the capacitor at a first node (A), the first terminal of the driving transistor being connected to the second terminal of the light emitting device and the second terminal of the capacitor at a second node (B), the second terminal of the driving transistor being connected to a controllable voltage supply line; a driver for driving the select line, the controllable voltage supply line and the signal line to operate the display array; the method including the steps of: at a programming cycle, at a first operating cycle, charging the second node at a first voltage defined by (VREF-VT) or (-VREF+VT), where VREF represents a reference voltage and VT represents a threshold voltage of the driving transistor; at a second operating cycle, charging the first node at a second voltage defined by (VREF+VP) or (-VREF+VP) so that the difference between the first and second node voltages is stored in the storage capacitor, where VP represents a programming voltage; at a driving cycle, applying the voltage stored in the storage capacitor to the gate terminal of the driving transistor.

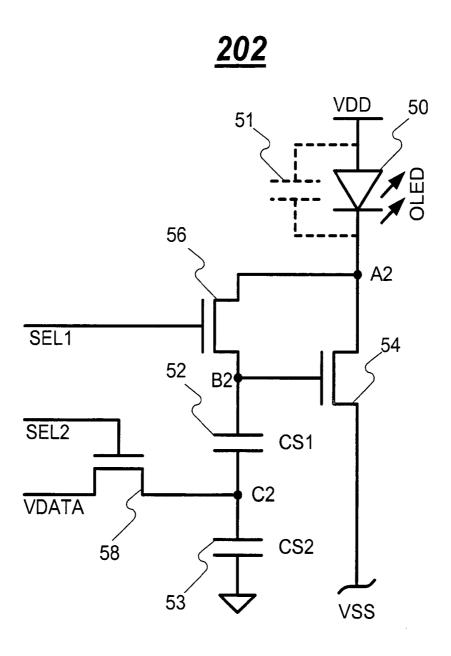

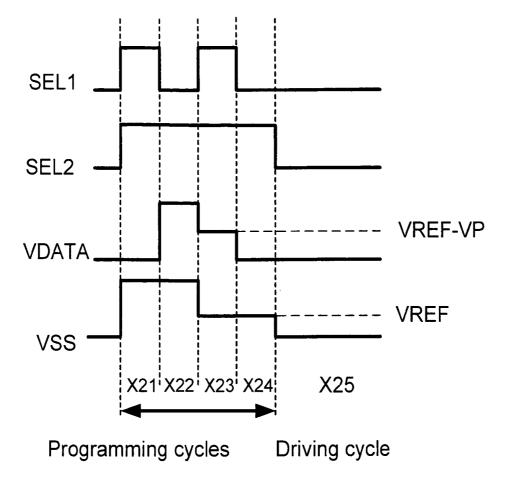

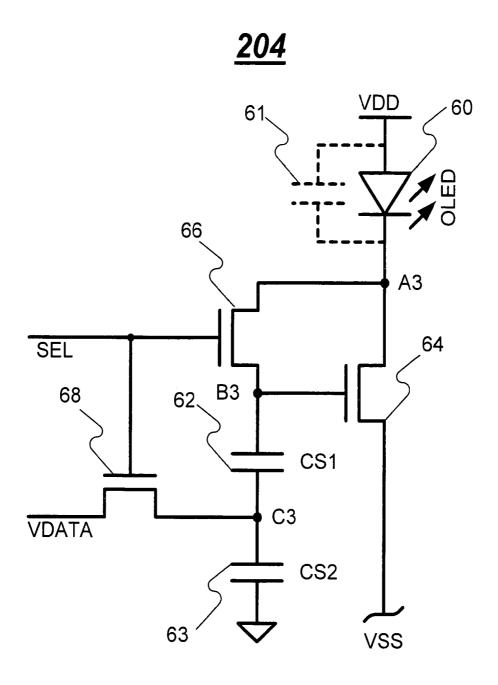

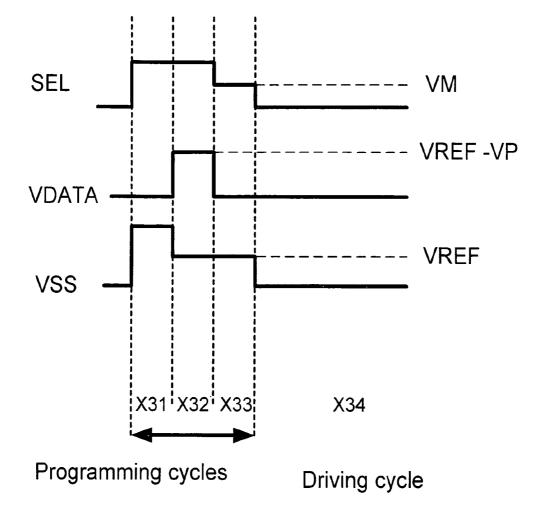

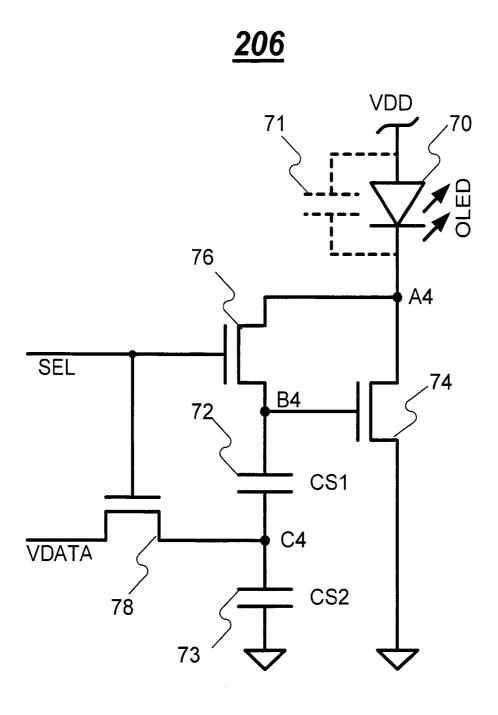

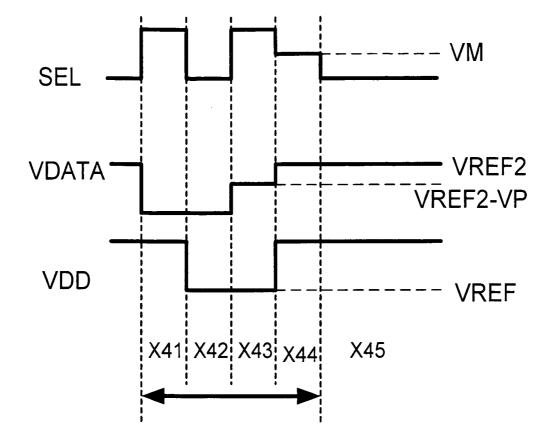

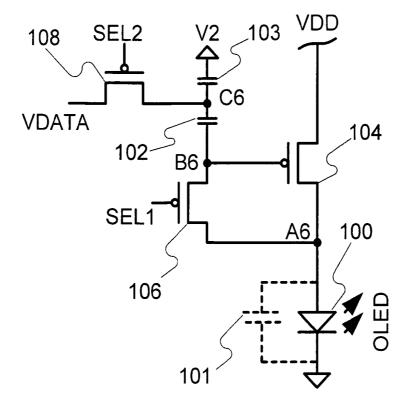

In accordance with a further aspect to the present invention there is provided a method of programming and driving a display system, the display system includes: a display array having a plurality of pixel circuits arranged in row and column, each pixel circuit having: a light emitting device having a first terminal and a second terminal, the first terminal of the lighting device being connected to a voltage supply electrode; a first capacitor and a second capacitor, each having a first terminal and a second terminal; a first switch transistor having a gate terminal, a first terminal and a second terminal, the gate terminal of the first switch transistor being connected to a first select line, the first terminal of the first switch transistor being connected to the second terminal of the light emitting device,

the second terminal of the first switch being connected to the first terminal of the first capacitor; a second switch transistor having a gate terminal, a first terminal and a second terminal, the gate terminal of the second switch transistor being connected to a second select line, the first terminal of the second 5 switch transistor being connected to a signal line for transferring voltage data; a driving transistor having a gate terminal, a first terminal and a second terminal, the first terminal of the driving transistor being connected to the second terminal of the light emitting device at a first node (A), the gate terminal of the driving transistor being connected to the second terminal of the first switch transistor and the first terminal of the first capacitor at a second node (B), the second terminal of the driving transistor being connected to a controllable voltage 15 supply line; the second terminal of the second switch transistor being connected to the second terminal of the first capacitor and the first terminal of the second capacitor at a third node (C); a driver for driving the first and second select line, the controllable voltage supply line and the signal line to operate 20 the display array, the method including the steps of: at a programming cycle, at a first operating cycle, controlling the voltage of each of the first node and the second node so as to store (VT+VP) or -(VT+VP) in the first storage capacitor, where VT represents a threshold voltage of the driving tran- 25 sistor, VP represents a programming voltage; at a second operating cycle, discharging the third node; at a driving cycle, applying the voltage stored in the storage capacitor to the gate terminal of the driving transistor.

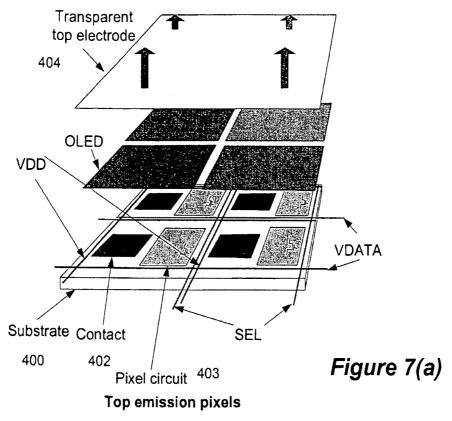

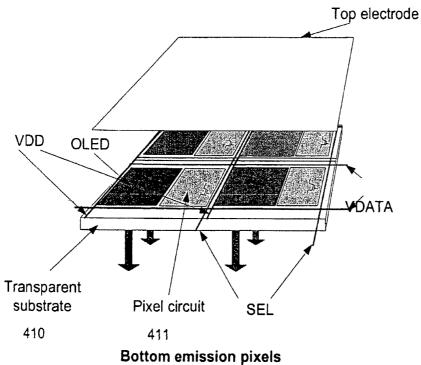

In accordance with a further aspect to the present invention 30 there is provided a display system including: a display array having a plurality of pixel circuits arranged in row and column, each pixel circuit having: a light emitting device having a first terminal and a second terminal, the first terminal of the lighting device being connected to a voltage supply electrode; 35 a capacitor having a first terminal and a second terminal; a switch transistor having a gate terminal, a first terminal and a second terminal, the gate terminal of the switch transistor being connected to a select line, the first terminal of the switch transistor being connected to a signal line for transferring 40 voltage data, the second terminal of the switch transistor being connected to the first terminal of the capacitor; and a driving transistor having a gate terminal, a first terminal and a second terminal, the gate terminal of the driving transistor being connected to the second terminal of the switch transis- 45 tor and the first terminal of the capacitor at a first node (A), the first terminal of the driving transistor being connected to the second terminal of the light emitting device and the second terminal of the capacitor at a second node (B), the second terminal of the driving transistor being connected to a con- 50 trollable voltage supply line; a driver for driving the select line, the controllable voltage supply line and the signal line to operate the display array; and a controller for implementing a programming cycle and a driving cycle on each row of the cycle includes a first operating cycle' and a second operating cycle, wherein at the first operating cycle, the second node is charged at a first voltage defined by (VREF-VT) or (-VREF+VT), where VREF represents a reference voltage and VT represents a threshold voltage of the driving transis- 60 tor, at the second operating cycle, the first node is charged at a second voltage defined by (VREF+VP) or (-VREF+VP) so that the difference between the first and second node voltages is stored in the storage capacitor, where VP represents a programming voltage; wherein at the driving cycle, the volt- 65 age stored in the storage capacitor is applied to the gate terminal of the driving transistor.